Explore the newly introduced Ryzen 9000 processors from AMD, complete with specifications and a confirmed release date. The Zenith 5 desktop series is set to debut in July (the upcoming month), featuring an upgraded frontend, broader memory subsystem, and enhanced AVX512 bandwidth. AMD touts an average increase of 16% in IPC, with the most noticeable improvements in tasks like Blender, Cinebench R23, League of Legends, and various content creation workloads. Let’s delve into the alterations within Zenith 5 and verify the accuracy of the previous leaks.

While the number of cores in the Ryzen 9000 family remains consistent, there have been no changes to the CPU’s boost clocks, and official confirmation is still pending regarding the L1/L2 cache. The total cache on the Ryzen 9 9950X stays at 80 MB, mirroring the 7950X, exclusive of the L1I and L1D cache content.

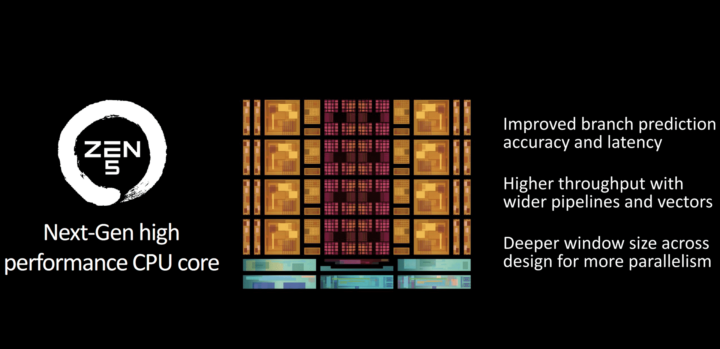

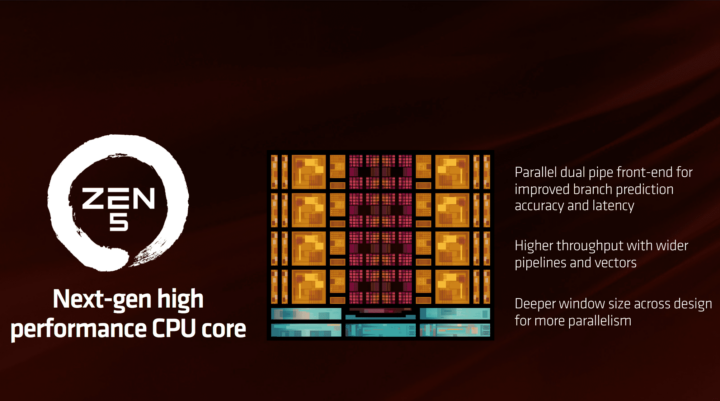

Unveiling the New Features of Zen 5

Speculations suggest that Zen 5 will elevate the L1D cache from 32KB to 48KB (12-way) with a 4-cycle load, accompanied by an expanded Data Translation Buffer and an optimized branch predictor. It’s likely that the L1I cache will retain its existing 32KB (8-way) capacity.

The upgraded branch predictor now boasts “enhanced prediction accuracy and latency.” Reports indicate that Zen 5’s branch predictor carries out “Zero bubble” conditional branches, suggesting zero disruption or halting of the pipeline during the execution of conditional branches.

Enhancements in the Core Components

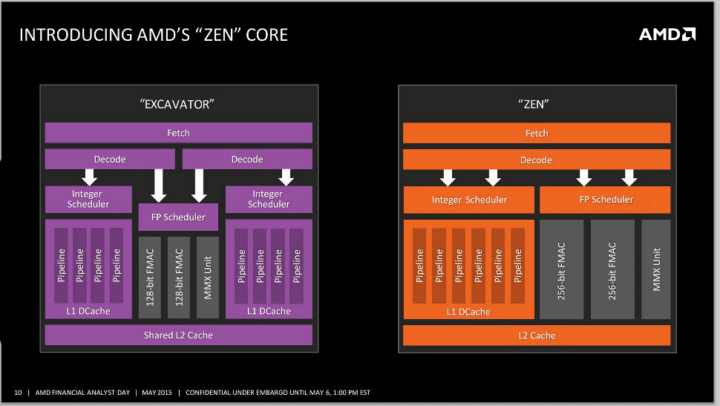

The decoder remains unchanged (4-way) with a 2-basic block fetch. The rename/dispatch buffer has undergone consolidation to concurrently process up to 8 micro-ops (formerly 6 micro-ops) while facilitating op-fusion. This fusion feature allows two micro-ops from a single instruction to be considered as one at specific pipeline stages, effectively doubling the operational throughput.

The Dispatch mechanism is also upgraded from 6 macro-ops on Zen 4 to 8 macro-ops on Zen 5, ensuring a consistently active backend. This suggests a doubled instruction bandwidth for frontend instructions, prompting questions about potential decoder expansions. Furthermore, the concept of the dual front-end implies an enhanced branch prediction accuracy and latency, with a focus on two frontend pipes per core.

References to expanded pipelines and vectors likely hint at broader execution capabilities. On the integer front, reports suggest the instruction scheduler has been strengthened into a unified queue with “larger structure sizes.” Smaller scheduler windows have been consolidated into larger queues, and the integer ALU count has been ramped up to 6 units (previously 4 units) to accommodate higher throughput.

For Floating Point operations, all four execution ports have purportedly doubled in width, reaching 512-bit to support AVX-512 instructions. Additionally, a fifth port comprising two 256-bit units has been integrated. The expanded Execution Units necessitate sizeable floating point registers for sustainable usage, notably larger than before. Notably, this feature might be exclusive to the Epyc cores, while the client Zen 5 variant could include the fifth FP port (256-bit).

Comparative Performance Insights

The performance gains over the Intel Core i9-14900 vary in gaming tasks from 4% in Borderlands to a substantial 23% in Horizon Zero Dawn. These improvements likely stem from an enhanced core interconnect (referred to as Ladder by AdoredTV), alongside the frontend and backend advancements impacting overall performance.

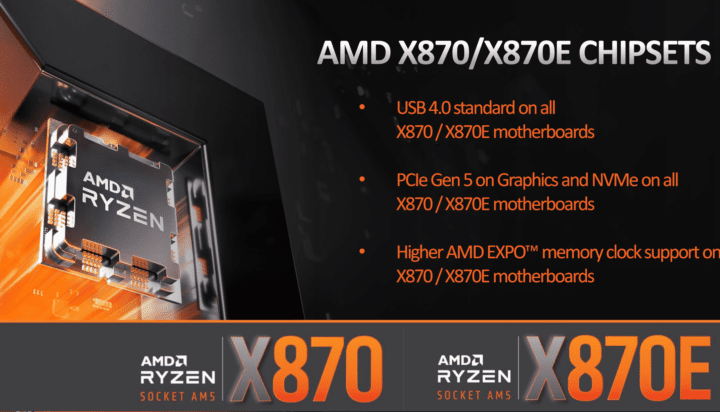

The X870/X870E chipsets show minimal divergence from the X670/X670E models. All dGPU and M.2 SSD slots (up to 24) have transitioned to PCIe Gen 5. Particularly noteworthy is the X870 chipset’s boost to accommodate up to 24 PCIe Gen 5 lanes, contrasting the previous 8x allocation on X670.

Anticipating Future Innovations

As per Kepler, the Ryzen 9000X3D processors (Zen 5 3D V-Cache) are earmarked for unveiling at CES 2025, slated for early January 2025. Considering the anticipated launch of the Ryzen 9000 “Zen 5” CPUs between summer and fall (June to September), maintaining a 6-month gap before the introduction of the 3D V-Cache variants appears plausible. This timeline may be influenced by Intel’s rollout of the 15th Gen Arrow Lake processors, which could impact market dynamics.

Frequently Asked Questions

- Are the Ryzen 9000 CPUs compatible with existing AM5 motherboards (A620/B650/B650E/X670/X670E)?

AMD has affirmed that the AM5 socket will remain supported through 2025. At a minimum, the current 600-series motherboards will be fully functional with the Ryzen 9000 CPUs, supported by firmware updates from board partners. Additionally, the upcoming 800-series motherboards will offer expanded I/O choices for non-X SKUs.

- When will the Ryzen 9000 CPUs be purchasable?

The Ryzen 9000 CPUs are slated for availability in July 2024.

- How do the Ryzen 9000 CPUs compare in speed to the 7000 series and Intel’s Raptor Lake range?

AMD’s Zen 5 core showcases an average 16% IPC boost. Performance enhancements in specific applications range between 10-35%, with a strong emphasis on content creation tasks.

For further insights: Dive into the details of AMD Zen 5 Strix Point/Halo, Granite Ridge & Turin: Ryzen 9000 Specifications, Updates & Rumors